# BYPASSING ASLR VIA SPECULATIVE BUFFER OVERFLOWS

Nicholas Mosier

Advisor: Professor Peter C. Johnson

A Thesis

Presented to the Faculty of the Computer Science Department of Middlebury College

May 2020

### ABSTRACT

Spectre, a class of speculative execution vulnerabilities disclosed in 2018, has demonstrated weaknesses in existing security protections. Attackers can exploit speculative buffer overflows, a Spectre variant, to achieve arbitrary speculative code execution in victims. The security community has not thoroughly explored which security protections speculative buffer overflows can bypass. Previous literature assesses that address space layout randomization (ASLR), a security protection in modern operating systems, effectively mitigates speculative buffer overflow attacks. I present SpectreR2P, a host-based attack that discloses a victim's ASLRrandomized code address via speculative buffer overflow, thereby demonstrating the ineffectiveness of ASLR against speculative buffer overflows.

## ACKNOWLEDGEMENTS

Peter C Johnson Shelby Kimmel Michael Linderman

## TABLE OF CONTENTS

| Intr | oduction                                                                                                                    | <b>2</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bac  | kground                                                                                                                     | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.1  | Execution on Modern Processors                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.1.1 Out-of-Order and Speculative Execution                                                                                | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.2  | The Cache                                                                                                                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.2.1 Cache Basics                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.2.2 L1, L2, and Shared L3 Caches                                                                                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.2.3 Cache Flushing and Prefetching                                                                                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.3  | Cache Timing Attacks                                                                                                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.3.1 General Approach                                                                                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | 2.3.2 Function Call Cache Probe                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.4  | Stack Attacks and Defenses                                                                                                  | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.4.1 Stack Buffer Overflows                                                                                                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.4.2 Return-Oriented Programming                                                                                           | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.4.3 Address Space Layout Randomization                                                                                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.5  | Spectre                                                                                                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 2.5.1 Spectre1.1: Speculative Buffer Overflows                                                                              | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.6  | Conclusion                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Мл   | Work: The Attack                                                                                                            | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| v    |                                                                                                                             | 21<br>21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -    |                                                                                                                             | $\frac{21}{23}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                             | $\frac{23}{23}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                             | $\frac{25}{25}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.4  |                                                                                                                             | $\frac{20}{25}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.5  | · · ·                                                                                                                       | $\frac{20}{27}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.0  |                                                                                                                             | $\frac{21}{28}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.6  |                                                                                                                             | $\frac{20}{28}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.0  |                                                                                                                             | $\frac{20}{30}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Č                                                                                                                           | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 5.5.5 Telaxing the rettack's timing requirements                                                                            | 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                                                                             | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                                                                             | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2  | Performance Metrics                                                                                                         | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.2.1 Measuring Accuracy                                                                                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.2.2 Measuring Runtime                                                                                                     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.3  |                                                                                                                             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.4  | Performance versus Background Activity                                                                                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

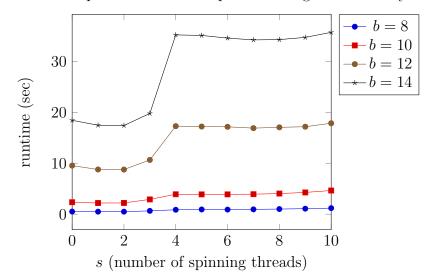

|      | 4.4.1 Runtime and Background Activity                                                                                       | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.4.2 Accuracy and Background Activity                                                                                      | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Bacl<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>My<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br><b>Resu</b><br>4.1<br>4.2 | Background         2.1       Execution on Modern Processors         2.1.1       Out-of-Order and Speculative Execution         2.2       The Cache         2.2.1       Cache Basics         2.2.2       L1, L2, and Shared L3 Caches         2.2.3       Cache Flushing and Prefetching         2.3       Cache Timing Attacks         2.3.1       General Approach         2.3.2       Function Call Cache Probe         2.4       Stack Attacks and Defenses         2.4.1       Stack Buffer Overflows         2.4.2       Return-Oriented Programming         2.4.3       Address Space Layout Randomization         2.5       Spectre         2.5.1       SPECTRE1.1: Speculative Buffer Overflows         2.6       Conclusion         My Work: The Attack         3.1       Attack Model         3.2       Attack Model         3.3       Attack Requirements and Constraints         3.4       Attack Components         3.5.1       Attack Overview         3.6.1       Timing Issues         3.6.2       Timing Parameters         3.6.3       Relaxing the Attack's Timing Requirements         3.6.3       Relaxing Accuracy |

|    | 4.5   | Perform | mance Compared to Previous Attacks |       |       |   |   |       |   |   | 41 |

|----|-------|---------|------------------------------------|-------|-------|---|---|-------|---|---|----|

|    |       | 4.5.1   | Comparing Time Until Success       |       |       |   |   |       |   |   | 42 |

|    |       | 4.5.2   | Improvements over Previous Attacks | <br>• | <br>• | • | • | <br>• | • | • | 43 |

| 5  | Con   | clusio  | 1                                  |       |       |   |   |       |   |   | 44 |

|    | 5.1   | Possib  | le Countermeasures                 |       |       |   |   |       |   |   | 44 |

|    |       | 5.1.1   | Previous work                      |       |       |   |   |       |   |   | 46 |

|    |       | 5.1.2   | Generalizability                   |       |       |   |   |       |   |   | 46 |

|    |       | 5.1.3   | Future Work                        | <br>• |       | • | • |       |   | • | 47 |

| Α  | Full  | Attac   | k and Victim Code                  |       |       |   |   |       |   |   | 49 |

|    | A.1   | Attack  | Code                               | <br>• |       | • | • |       |   | • | 49 |

| Bi | bliog | raphy   |                                    |       |       |   |   |       |   |   | 57 |

## LIST OF TABLES

| 2.1 | Cache hierarchy                                           | 3 |

|-----|-----------------------------------------------------------|---|

| 2.2 | 64-bit ASLR-randomized virtual address                    | 3 |

| 2.3 | ASLR on macOS                                             | 3 |

| 3.1 | Guess terminology                                         | ) |

| 3.2 | Attack synchronization issues                             | 2 |

| 4.1 | Test workstation specifications                           | 3 |

| 4.2 | Attack performance results with no background activity 37 | 7 |

| 4.3 | Previous attack comparison                                | 3 |

## LIST OF FIGURES

| 2.1 | Stack buffer overflow example.                   | 12 |

|-----|--------------------------------------------------|----|

| 2.2 | ROP attack example                               | 14 |

| 2.3 | Speculative buffer overflow example              | 18 |

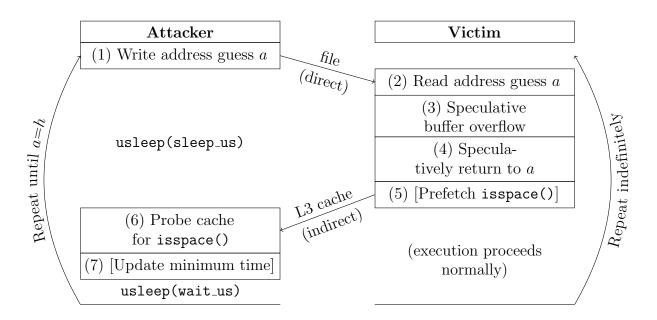

| 3.1 | Attack control flow diagram                      | 22 |

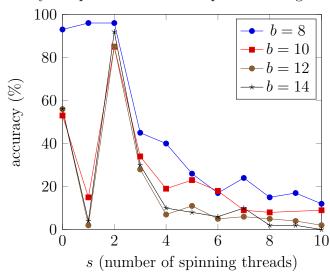

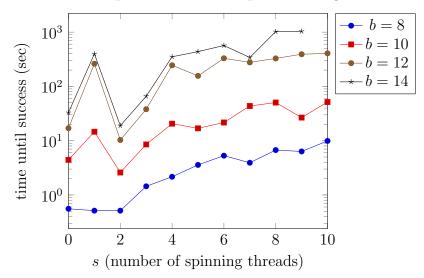

| 4.1 | Attack runtime vs. spinning threads              | 39 |

| 4.2 | Attack runtime vs. background threads            | 40 |

| 4.3 | Attack time until success vs. background threads | 42 |

## LIST OF LISTINGS

| 2.1 | Speculative execution example (C)                                                              | 6  |

|-----|------------------------------------------------------------------------------------------------|----|

| 2.2 | Speculative execution example (x86)                                                            | 6  |

| 2.3 | Basic cache probe (C)                                                                          | 9  |

| 2.4 | Basic cache probe (x86)                                                                        | 9  |

| 2.5 | Function call cache probe (C) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 10 |

| 2.6 | Function call cache probe (x86)                                                                | 10 |

| 2.7 | Stack buffer overflow source                                                                   | 12 |

| 2.8 | Example Spectre1.1 vulnerability (C).                                                          | 18 |

| 2.9 | Example Spectre1.1 vulnerability (x86)                                                         | 18 |

| 4.1 | Successful run of SpectreR2P in the shell                                                      | 35 |

| 4.2 | Background spinning thread                                                                     | 38 |

| A.1 | Attack source code (C)                                                                         | 49 |

| A.2 | Attack source code (x86)                                                                       | 52 |

| A.3 | Victim source (x86)                                                                            | 53 |

| A.4 | Victim source (C)                                                                              | 55 |

| A.5 | ASLR utility script                                                                            | 55 |

## CHAPTER 1 INTRODUCTION

The recent discovery of the Spectre hardware vulnerability has brought into question the effectiveness of existing security methods. Following Spectre's discovery in 2018 [6], security researchers have discovered a multitude of Spectre variants [7, 5], each with serious implications similar to Spectre. However, the security community has not thoroughly explored to what extent attackers can use new Spectre variants to break existing security protections. Specifically, it is unknown whether speculative buffer overflows, Spectre v1.1, are able to defeat address space layout randomization (ASLR), a security protection of all modern operating systems that randomizes a program's addresses at runtime.

In this thesis, I present SpectreR2P ("Spectre Return to Prefetch"), an attack that uses a speculative buffer overflow to disclose the randomized runtime address of a victim process' instructions. The success of SpectreR2P demonstrates that an attacker can use a speculative buffer overflow vulnerabilities can to bypass ASLR.

In Chapter 2, I discuss background information required to understand SpectreR2P. In Chapter 3, I introduce SpectreR2P and describe how it works in detail. In Chapter 4, I present performance results of SpectreR2P and compare it to a previous attack.

#### Motivation

Spectre affects all modern processors: it is the product of the ability of speculative execution to modify the state of the cache, even during misspeculation. These two features, speculative execution and the cache, are essential optimizations for modern processors. Spectre affects all modern processors, including Intel's x86-64 processors (found in most personal computers) and ARM processors (found in virtually all smartphones). Furthermore, Spectre vulnerabilities affect all programs, even those that are bug-free and written correctly. This is because Spectre exploits adverse interactions between speculative execution and the cache at the microarchitectural level, rather than the semantic correctness level. The most effective protections against Spectre to date are software mitigations that require program recompilation [13]; binaries compiled without Spectre mitigation remain vulnerable.

Speculative buffer overflows, a variant of the Spectre vulnerability discovered by Kiriansky et al. [5], open up an even wider range of attack methods than the first Spectre variant [6]. The attacker can adapt existing attacks that target non-speculative buffer overflows to speculative buffer overflows.

Address space layout randomization (ASLR) is an essential security protection in modern operating systems and existing literature believes it protects against speculative buffer overflows.<sup>1</sup> If a speculative-buffer-overflow-based attack can in fact defeat ASLR, however, the attacker can use the traditional exploitation techniques that ASLR protects against, such as return-oriented programming (Section 2.4.2), to achieve arbitrary code execution in the victim.

#### My Contributions

I present SpectreR2P, an attack that exploits a speculative buffer overflow that discloses the randomized runtime address of a victim process with ASLR enabled. The success of SpectreR2P demonstrates that ASLR is in fact ineffective against speculative buffer overflow vulnerabilities under particular conditions (Section 3.3). My work therefore demonstrates that the original assessment of Kiriansky et al. [5] underestimates the ability of speculative buffer overflows and overestimates the effectiveness of ASLR against speculative buffer overflows.

$<sup>^1{\</sup>rm Kiriansky}$  et al. [5] claim that "[ASLR] is the only generic mitigation currently available against speculative buffer overflows."

## CHAPTER 2 BACKGROUND

SpectreR2P builds on top of existing speculative execution attacks, employs existing cache timing attack methods, and adapts existing attacks strategies.

## 2.1 Execution on Modern Processors

Modern processors implement many optimizations over a sequential processor; however, they still obey a sequential execution model. Processors have two levels of abstraction: the *instruction set architecture* and the *microarchitecture*.

A processor's instruction set architecture (ISA), or just "architecture", describes the programmable interface provided by the processor, including the instructions semantics, the register set, and the abstract execution model. Intel's x86-64 ISA has 64-bit registers and addresses, defines a sequential execution model: the effects of previous instructions become visible before the effects of any following instructions.

A processor's microarchitecture ( $\mu$ arch) describes the particular implementation of the processor's corresponding ISA. The microarchitecture must meet the specifications of the ISA. Modern microarchitectures are heavily optimized, employing out-of-order, superscalar, and speculative execution. However, such microarchitectures must make the program *appear* to execute sequentially. Nevertheless, a program can observe side-effects inconsistent with sequential execution in the cache through timing instructions, as we will see in Sections 2.3 and 2.5.

## 2.1.1 Out-of-Order and Speculative Execution

Out-of-order execution is a microarchitectural optimization that allows the processor to execute instructions in a different order than in which they appear, while maintaining the appearance of sequential execution. Some instructions are high-latency and require many processor cycles to complete. Rather than stalling during that long period, the processor will instead execute subsequent instructions that do not depend upon the result of the highlatency instruction, covering its high latency and increasing processor instructions per cycle (IPC). Processors with out-of-order execution may execute instructions out of order as long as doing so does not affect the program state.

Control flow instructions, e.g., conditional branches, often depend on operands that may not yet be available. Rather than waiting for the operands to become available, modern processors will *speculate* the direction of control flow and proceed to *speculatively execute* the instructions along that path. Once the control flow operand becomes available, the processor either (i) commits the results of the speculative execution and resumes non-speculative execution where the speculative execution left off, if the guess was correct, or (ii) discards the results of the speculative execution and resumes non-speculative execution at the control flow instruction, if the guess was incorrect. In the latter case, we say that the processor *misspeculated*, and it *misspeculatively executed* the wrong execution path. Misspeculative execution is the transient kind of speculative execution: the processor always discards its results. Furthermore, whenever speculative execution encounters an error, such as an invalid memory access, the processor rolls back the speculative execution context to the closest non-speculative context. <sup>1</sup> Therefore, misspeculation has no effect on program state.

Listings 2.1 and 2.2 include code examples that may cause (mis)speculative execution. The program takes the conditional branch in Listing 2.2 99 out of 100 times. Suppose that the processor always speculatively takes the branch if the result of the comparison operation cmp is not yet available. For the first 99

<sup>&</sup>lt;sup>1</sup>In contrast, a non-speculative invalid memory access triggers a segmentation fault and the process may terminate.

```

for (int i = 0; i < 100; ++i)

;

return;</pre>

```

Listing 2.1: Basic C for loop

Listing 2.2: Basic x86 for loop

loop iterations, the processor speculates correctly and thus commits the results of speculative execution once cmp resolves. On the last iteration, however, the processor misspeculates and subsequently discards the results of the misspeculative execution before reverting to the correct execution path starting with the ret instruction.

The *branch predictor* is the processor component that guesses whether the processor should take a given branch during speculative execution. Modern processors have other prediction components, such as the return stack buffer (RSB), which correspond to different instructions and scenarios.

Section 2.5 presents a class of misspeculative execution vulnerabilities, which the attack I present exploits.

### 2.2 The Cache

Caches are an essential feature not only to modern processors but also to modern attacks. The attack I present uses the cache as a side-channel by causing the victim to leak information through the cache to the attacking process.

### 2.2.1 Cache Basics

Accesses to main memory frequent but slow, on the order of 100 ns [9]. This is a result of both the trade-offs made in the underlying medium (most commonly capacitor-based DRAM) and the physical distance separating memory from the CPU. The processor minimizes how much memory access throttles execution by *caching* recently accessed memory regions in a memory bank that is closer to the CPU and faster than main memory. This memory bank is the *cache*. The *cache line* is the unit of contiguous memory around an accessed value that the processor brings into the cache along with the accessed value. On modern processors, cache lines are generally 64 bytes in size.

A cache hit occurs when the CPU issues a memory access to memory contents already present in the cache; a cache miss occurs when the CPU issues a memory access not present in the cache. A cache miss is an order of magnitude slower than a cache hit, since the former entails accessing main memory, while the latter only involves accessing the cache. The timing difference is great enough that it can be consistently measured using a high-resolution clock, which cache-timing attacks can exploit, including the one I present.

## 2.2.2 L1, L2, and Shared L3 Caches

In modern CPUs, "the cache" is actually a cache hierarchy of two or three different levels, in order of increasing capacity and latency: the L1, L2, and L3 cache. Each processor core has its own private L1 and L2 caches, but all cores share the same L3 cache (on most processors). The shared L3 cache has important security implications: on a multi-core processor, one process can track the memory accesses of another process through observing cache hits and cache misses while accessing data occupying the same L3 cache lines as the other process' data.

In the attack I present, the attacker and victim must share a cache. Since all cores share the L3 cache, the attack works as long as the attacker and victim processes run on the same processor but on potentially different cores.

| Level | Sharing | Latency (cycles) | Latency $(ns)^2$ |

|-------|---------|------------------|------------------|

| L1    | private | 4                | 1                |

| L2    | private | 10               | 3                |

| L3    | shared  | 65               | 30               |

Table 2.1: The cache hierarchy [8].

## 2.2.3 Cache Flushing and Prefetching

Intel's X86 instruction set gives the programmer the ability to directly manipulate the cache through the clflush and prefetch instructions. The clflush instruction evicts the cache line containing the memory value operand so that subsequent accesses within that cache line generate cache misses. The prefetch instruction preforms the opposite operation: it brings the memory value operand (and its associated cache line) into the cache.

These cache instructions are unique in that they have no effect on architectural state; they operate at the microarchitectural level. This simultaneously potential optimization opportunities as well as potential security issues. clflush and prefetch are essential to cache-timing attacks (Section 2.3).

## 2.3 Cache Timing Attacks

From an attacker's perspective, the cache contains an imperfect record of a victim's memory accesses. Attackers can recover information about the victim's memory access patterns by using a *cache timing attack*. A cache timing attack involves timing accesses to the cache and from those access times inferring whether particular memory regions are in the cache. An attacker can use a cache timing attack to leak the victim's secrets.

<sup>&</sup>lt;sup>2</sup>Assuming a clock frequency of 3.0GHz, which is common for Intel i7 processors.

```

#define THRESH <threshold>

/* probe whether *addr

* in cache */

int probe(char *addr) {

int start = __rdtsc();

char c = *addr;

int stop = __rdtsc();

return

stop - start < THRESH;

}</pre>

```

Listing 2.3: Basic method of probing cache for address (C).

```

%define THRESH <threshold>

;; probe whether [rdi]

;; in cache

probe:

rdtsc

mov edx,eax

mov bl,[rdi]

rdtsc

sub eax,edx

cmp eax,THRESH

mov eax,0

cmovl eax,1

ret

```

Listing 2.4: Basic method of probing cache for address (x86 asm).

## 2.3.1 General Approach

The simplest cache timing attack recovers 1 bit of information from the attacker: whether it has recently accessed data at a given address. Let the data be at address A, and suppose the attacker wants to determine whether a victim function Faccesses data at A. The attack then proceeds as follows:

- 1. Flush the cache line containing A.

- 2. Induce the victim process to execute F.

- 3. Probe the cache for data at A.

Probing the cache (Item 3) requires further explanation.

#### Memory Read Cache Probe

The simplest cache probe of address A is to time a memory read from A using x86's time-stamp counter, accessed through the rdtsc instruction [4]. Listings 2.3 and 2.4 presents a minimal example of this simple cache probe.

More sophisticated cache timing attacks use this memory read cache probe method [14, 15].

```

#define THRESH <threshold>

/* probe whether *addr

* in cache */

int probe(void (*func)(void)) {

int start = __rdtsc();

func();

int stop = __rdtsc();

return

stop - start < THRESH;

}</pre>

```

Listing 2.5: Function call method of probing cache for instructions (C).

```

%define THRESH <threshold>

probe whether [rdi]

in cache

probe:

rdtsc

push rax

call

rdi

rdtsc

pop rdx

eax,edx

eax, THRESH

cmp

mov eax,0

cmovl eax,1

ret

```

Listing 2.6: Function call method of probing cache for instructions (x86 asm).

## 2.3.2 Function Call Cache Probe

An alternative approach to the cache probe presented in Section 2.3.1 is to *call* address A and time the function's execution rather than reading directly from A and timing the read. Executing an instruction involves reading it from memory first, so a function with cached instructions executes faster than a function with uncached instructions. Probing the presence of instructions in the cache via a direct read and via a function call are roughly equivalent. This approach only works if address A points to executable instructions, which are only found in the victim's code or a shared library. In SpectreR2P, the attacker and victim share the C standard library libc, and the attacker chooses A = isspace. See Listings 2.5 and 2.6 for a minimal example of a function call cache probe.

The advantage to the function call approach is that it is less susceptible to noise than the direct read approach and it requires less clock precision, since the timing differences of cache hits versus cache misses accumulate over the execution of the probed instructions. ARM processors lack a high-precision time-stamp instruction like x86's rdtsc, making it difficult to differentiate cache hits versus cache misses during a single memory read. Therefore, the function call approach is more feasible than the memory read approach on ARM processors. Zhang et al. demonstrate that a similar approach involving executing sparse instructions using return-oriented techniques (Section 2.4.2) is successful on ARM. While SpectreR2P specifically targets the x86-64 architecture, Zhang et al.'s findings demonstrate it may be adaptable to ARM as well.

## 2.4 Stack Attacks and Defenses

Over the two decades, an arms race between attacks and defenses has unfolded. Attacks and defenses have grown in complexity with time, but modern attack strategies derive from old attack strategies.

In the following attacks, the ultimate goal of the attacker is to achieve *arbitrary code execution* in the victim. My attack seeks to disable a particular defense (address space layout randomization) that protects against a particular attack strategy (return-oriented programming) that achieves arbitrary code execution in the victim. Furthermore, my attack borrows strategies from stack buffer overflow vulnerabilities and return-oriented programming, applying them to a speculative execution context.

### 2.4.1 Stack Buffer Overflows

A *buffer overflow* is a bug in which a process erroneously writes past the end of an allocated memory region, e.g., an array. In languages without implicit array bounds checking, e.g., C and C++, flaws in program logic can cause a process to write data past the end of the array. Most commonly this occurs when the process fills a fixed-length buffer with variable-length data. For example, a call to the C standard library's char \*strcpy(char \*dst, char \*src), which copies string

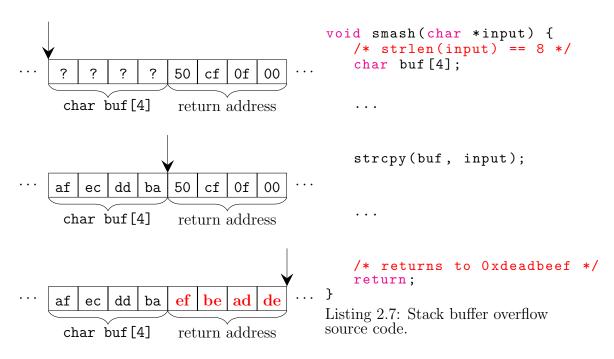

Figure 2.1: Example of a stack buffer overflow. An unbounded strcpy() causes the current function to return to the address Oxdeadbeef rather than Ox000fcf50.

src into buffer dst, triggers a buffer overflow within strcpy() when the length of src exceeds the allocated size of dst.<sup>3</sup>

A process' call stack contains a series of *stack frames*. A *stack frame* consists of the callee function's local variables, the return address into the caller function, and the parameters passed from the caller to the callee. Since program data and control data are stored adjacently on the stack, writing program data out of bounds on the stack can corrupt the control data. Therefore, the overflow of a buffer located on the stack can corrupt the callee function's return address so that it returns to a new location. This is often called *smashing the stack*. If the new, corrupted return address is invalid, then the callee's return generates a segmentation fault. If the corrupted return address is valid, however, the callee successfully returns to and then executes the instructions at that address. If an attacker controls the data written to the stack buffer, she controls the new return address of the callee and

<sup>&</sup>lt;sup>3</sup>strcpy() can still be used safely, however. To witness the *real* horrors of buffer overflows, look no further than the C standard library's now-deprecated gets() function.

thus the subsequent execution of the victim.

Fig. 2.1 depicts a stack buffer overflow.<sup>4</sup> The function smash() contains a stack buffer overflow vulnerability: it declares a *byte* 4 buffer **buf** on the stack, but copies an unbounded amount of data into the buffer in its call to strcpy(). To exploit this vulnerability, an attacker can supply an input string of length *bytes* 8. Since the length of input exceeds the length of **buf**, it triggers a stack buffer overflow, causing the victim to overwrite its return address on the stack with the last *bytes* 4 of the attacker-controlled input. In the example, the victim returns to the attackerdefined address Oxdeadbeef. See Aleph One's seminal article "Smashing the stack for fun and profit" [10] for details on stack smashing and its origins.

The simplest kind of stack-smashing attack overflows the victim's buffer with malicious instructions in addition to a new return address that points to those instructions. The victim returns to and then executes the malicious instructions on the stack. To protect against this attack strategy, operating systems introduced the W<sup>X</sup> protection (read "write xor execute"): segments may be either writable or executable, but never both.<sup>5</sup> Consequently, attackers cannot write to the victim's executable segments, rendering stack smashing impossible. Attackers responded with code-reuse attacks, exemplified by the following attack paradigm.

## 2.4.2 Return-Oriented Programming

Return-oriented programming (ROP) attacks exploit stack buffer overflow vulnerabilities by injecting a sequence of so-called *gadgets* into a victim process' stack frame. *Gadgets* are short series of instructions traditionally ending in a return instruction (ret) that the attacker can chain together to perform arbitrary computation in

$<sup>^4{\</sup>rm The}$  example assumes 32-bi addresses for simplicity. My attack targets Intel's x86-64 ISA, which has 64-bit addresses.

<sup>&</sup>lt;sup>5</sup>Yes,  $\sim$ (W&X) would have been a more accurate name.

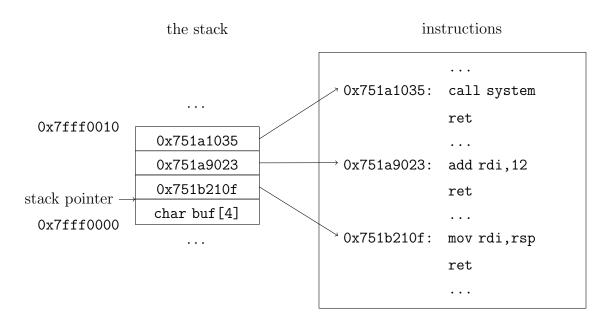

Figure 2.2: Example of a ROP attack. The attacker has corrupted the victim's stack with gadget addresses.

the in the victim [11]. However, the attacker can only use gadgets in the victim's code segment or shared libraries because under W<sup>X</sup>, the victim cannot execute the stack or any other writable segment.